V53C318165A70 Просмотр технического описания (PDF) - Mosel Vitelic, Corp

Номер в каталоге

Компоненты Описание

Список матч

V53C318165A70 Datasheet PDF : 18 Pages

| |||

MOSEL VITELIC

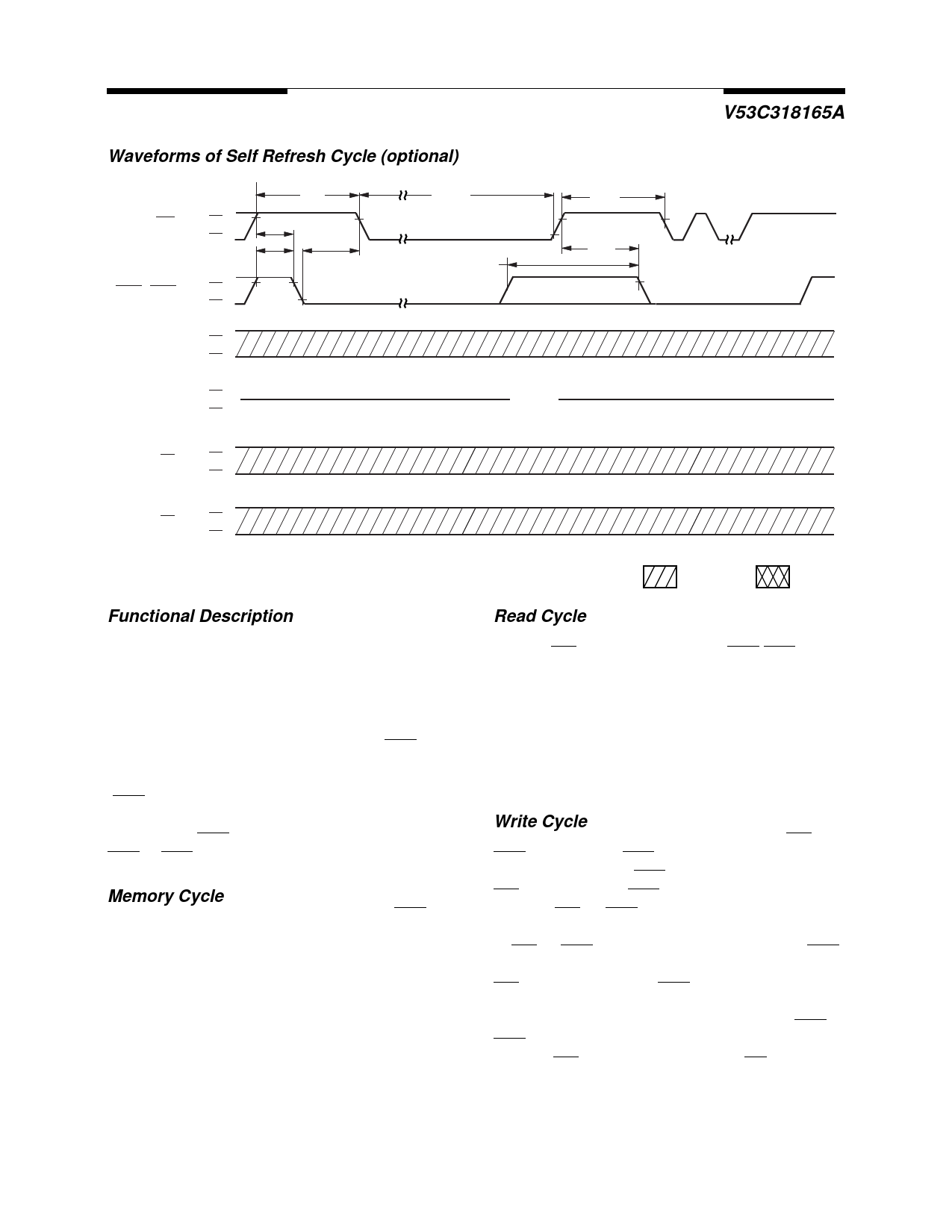

Waveforms of Self Refresh Cycle (optional)

RAS VIH

VIL

UCAS, LCAS VIH

VIL

tRP

tRPC

tCP

tCSR

tRASS

tCHS

ADDRESS VIH

VIL

tRPS

tRPC

I/O VOH

VOL

OPEN

V53C318165A

WE VIH

VIL

OE VIH

VIL

Functional Description

The V53C318165A is a CMOS dynamic RAM op-

timized for high data bandwidth, low power applica-

tions. It is functionally similar to a traditional

dynamic RAM. The V53C318165A reads and writes

data by multiplexing an 20-bit address into a 10-bit

row and a 10-bit column address. The row address

is latched by the Row Address Strobe (RAS). The

column address “flows through” an internal address

buffer and is latched by the Column Address Strobe

(CAS). Because access time is primarily dependent

on a valid column address rather than the precise

time that the CAS edge occurs, the delay time from

RAS to CAS has little effect on the access time.

Memory Cycle

A memory cycle is initiated by bringing RAS low.

Any memory cycle, once initiated, must not be end-

ed or aborted before the minimum tRAS time has ex-

pired. This ensures proper device operation and

data integrity. A new cycle must not be initiated until

the minimum precharge time tRP/tCP has elapsed.

Don’t Care

311816500-17

Undefined

Read Cycle

A Read cycle is performed by holding the Write

Enable (WE) signal High during a RAS/CAS opera-

tion. The column address must be held for a mini-

mum specified by tAR. Data Out becomes valid only

when tOAC, tRAC, tCAA and tCAC are all satisifed. As

a result, the access time is dependent on the timing

relationships between these parameters. For exam-

ple, the access time is limited by tCAA when tRAC,

tCAC and tOAC are all satisfied.

Write Cycle

A Write Cycle is performed by taking WE and

CAS low during a RAS operation. The column ad-

dress is latched by CAS. The Write Cycle can be

WE controlled or CAS controlled depending on

whether WE or CAS falls later. Consequently, the

input data must be valid at or before the falling edge

of WE or CAS, whichever occurs last. In the CAS-

controlled Write Cycle, when the leading edge of

WE occurs prior to the CAS low transition, the I/O

data pins will be in the High-Z state at the beginning

of the Write function. Ending the Write with RAS or

CAS will maintain the output in the High-Z state.

In the WE controlled Write Cycle, OE must be in

the high state and tOED must be satisfied.

V53C318165A Rev. 1.0 January 1998

14