CS5513-BS(2000) Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS5513-BS Datasheet PDF : 26 Pages

| |||

VD+ = 2.5 V to 5.25 V

Fairchild NC7SU04

or 1/6 74HCU04

To SCLK

47 pF

10 MΩ

32.768 kHz

49.9 KΩ

22 pF

CS5510/11/12/13

SCLK

CS5510/12

SDO

CS

Counter/Timer

µC

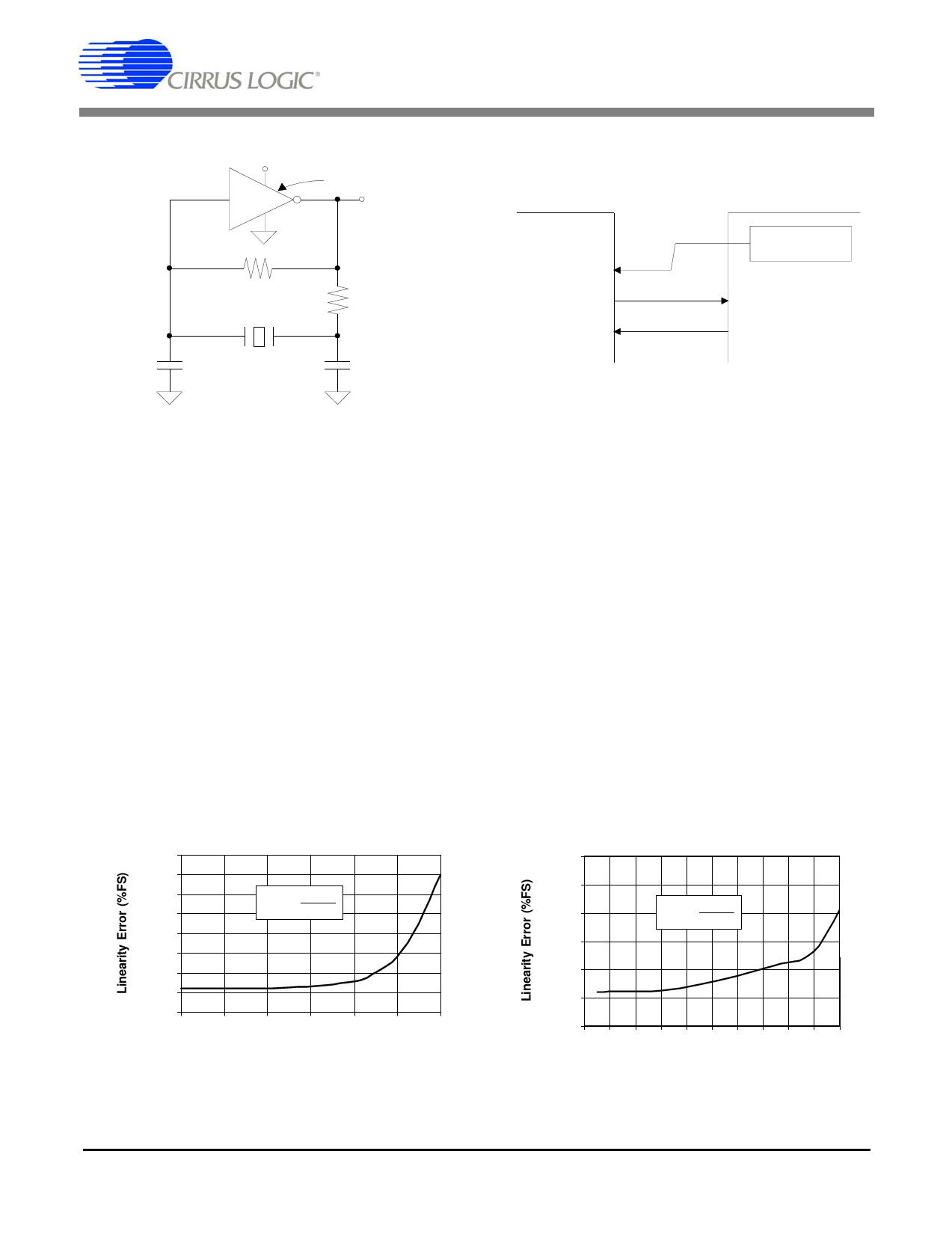

Figure 12. External (CMOS Compatible) Clock Source. Figure 13. Using a Microcontroller as a Clock Source.

Note that the CS5510 can operate with an external

(CMOS compatible) clock at frequencies up to

130 kHz, and the CS5512 can operate with an ex-

ternal clock of up to 200 kHz with a maximum

22ns of jitter. Linearity performance is degraded

slightly with higher clock speeds, as shown in

Figures 14 and 15. The noise performance of the

parts, however, is not affected by higher clock

speeds.

2.4.2 Internal Oscillator for CS5511/13

The CS5511/13 includes an on-chip oscillator. This

oscillator provides the master clock for the

CS5511/13 and oscillates at 64 kHz ±32 kHz. The

output word rate (OWR) for the CS5511/13 is de-

rived from the internal oscillator, and is equal to

fosc/612. Due to the part-to-part variances in the os-

cillator frequency, the OWR of the CS5511/13 can

vary between 53 Hz and 159 Hz.

0.004

0.0035

0.003

0.0025

OWR = SCLK

612

0.002

0.0015

0.001

0.0005

0

10 30 50 70 90 110 130

SCLK (kHz)

Figure 14. Typical Linearity Error for CS5510.

DS337F1

0.003

0.0025

0.002

0.0015

OWR = SCLK

612

0.001

0.0005

0

0 20 40 60 80 100 120 140 160 180 200

SCLK (kHz)

Figure 15. Typical Linearity Error for CS5512.

15