CS5516-AP Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS5516-AP Datasheet PDF : 41 Pages

| |||

CS5516, CS5520

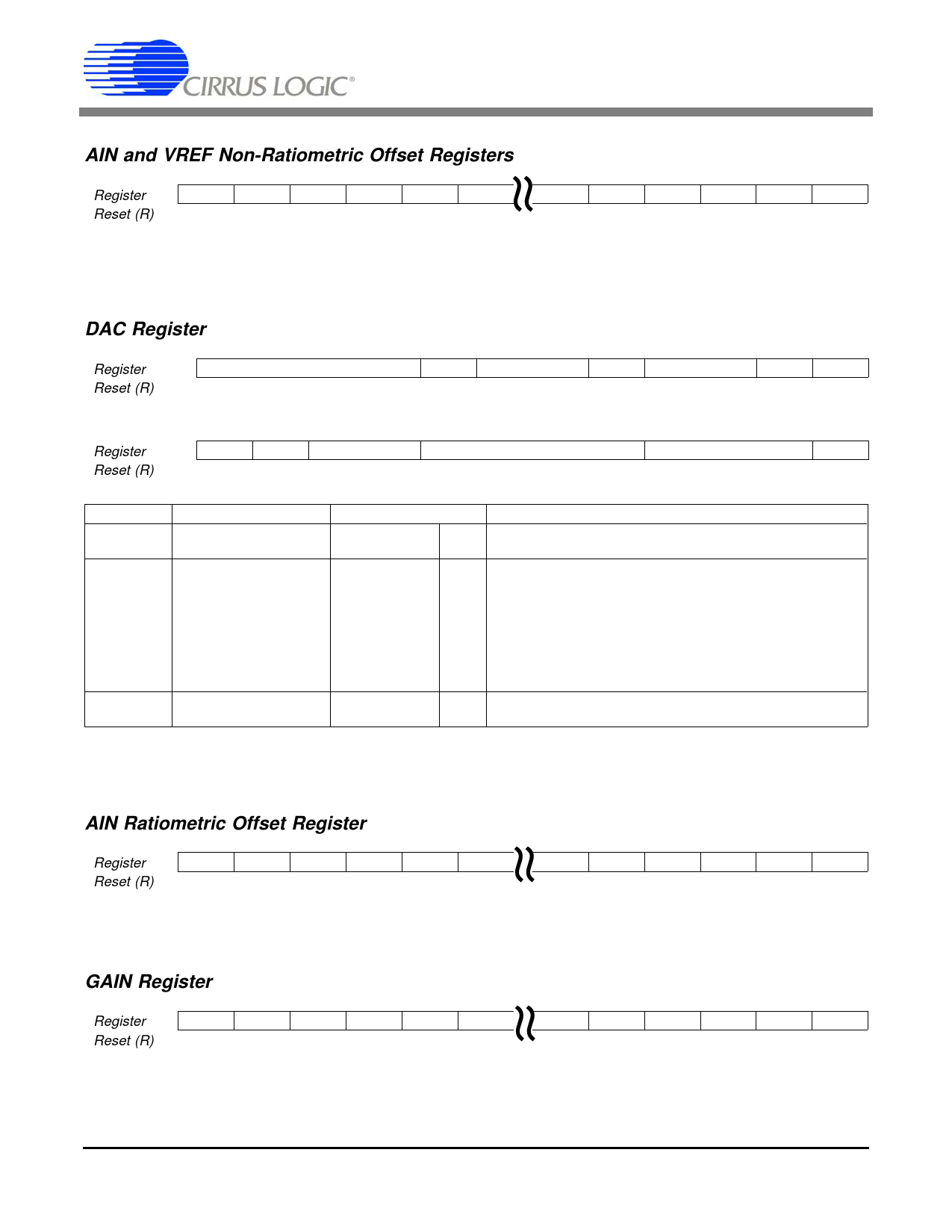

AIN and VREF Non-Ratiometric Offset Registers

Register

MSB

20

2-1

2-2

2-3

2-4

2-5

Reset (R)

0

0

0

0

0

0

LSB

2-18

2-19

2-20

2-21

2-22

2-23

0

0

0

0

0

0

One LSB represents 2-23 proportion of the internal MDRV (≈2.5 Volts)

DAC Register

D23 D22 D21 D20 D19 D18 D17 D16 D15 D14 D13 D12

Register

DAC3 DAC2 DAC1 DAC0 EXC F1

F0 D16 G1

G0 U/B D12

Reset (R)

0

0

0

0

0

0

0

0

0

0

0

0

Register

Reset (R)

D11 D10 D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

A/S EC

D9

D8 CC3 CC2 CC1 CC0 D3

D2

D1

RF

0

0

0

0

0

0

0

0

0

0

0

0

BIT

DAC3

DAC2-0

NAME

DAC Sign Bit

DAC Bits

Bits

D19 to D0

VALUE

0

R1

1

000

R

001

010

011

100

101

110

111

0

R

Add Offset

Subtract Offset

FUNCTION

25% Offset

50% Offset

75% Offset

100% Offset

125% Offset

150% Offset

175% Offset

These bits mirror the

Configuration Register

read only2

Note: 1. Reset State

2. A write to these bits does not change the register bit values.

AIN Ratiometric Offset Register

Register

MSB

20

2-1

2-2

2-3

2-4

2-5

Reset (R)

0

0

0

0

0

0

LSB

2-18

2-19

2-20

2-21

2-22

2-23

0

0

0

0

0

0

One LSB represents 2-23 proportion of the voltage [<(VREF+) - (VREF-)>/GAIN] where GAIN = 25 X PGA Gain

GAIN Register

Register

MSB

20

2-1

2-2

2-3

2-4

2-5

Reset (R)

1

0

0

0

0

0

LSB

2-18

2-19

2-20

2-21

2-22

2-23

0

0

0

0

0

0

The gain register span from 0 to (2-2-23). After Reset the MSB=1, all other bits are 0.

Table 4. Calibration Registers

1188

DS74F21