HCD66764BP Просмотр технического описания (PDF) - Hitachi -> Renesas Electronics

Номер в каталоге

Компоненты Описание

Список матч

HCD66764BP Datasheet PDF : 38 Pages

| |||

HD66764

Instructions

Outline

The HD66764 has seven internal registers. The data is written to these registers by using a common

serial data interface. This interface can be directly connected with the HD66763 segment driver for the

automatic transfer of instructions. When an instruction is written to the HD66763 via the bus from the

CPU, it is output from the serial interface of the HD66763, and the HD66764 receives the instruction to

make a setting in one of its internal registers.

In the bit configuration for the transfer of instructions, the upper three bits are index numbers that

indicate the target register of the transfer, and the lower 13 bits are the data.

Detailed Description

Power Control 1

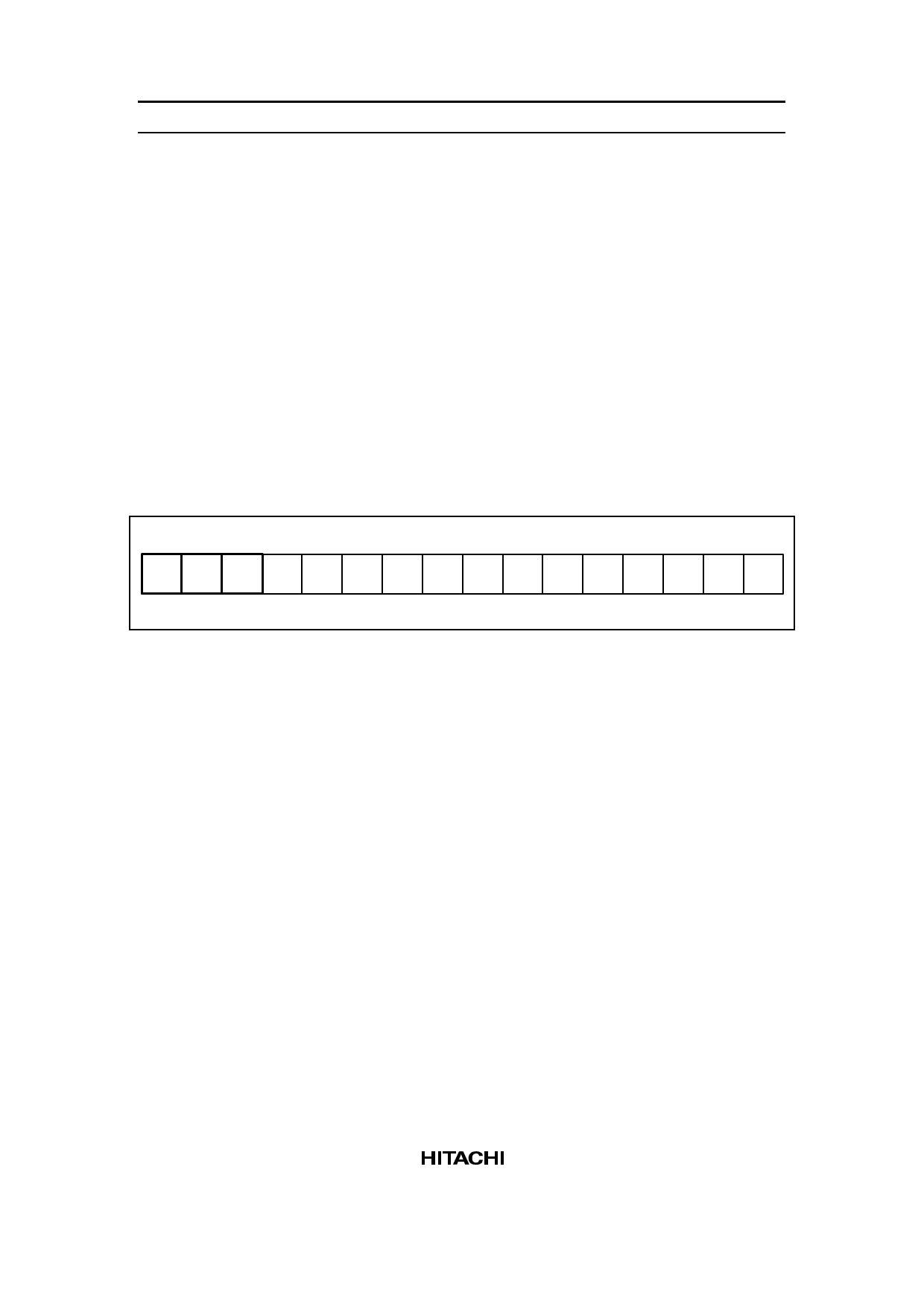

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

0

0

0 BS2 BS1 BS0 BT3 BT2 BT1 BT0 DC2 DC1 DC0 AP1 AP0 SLP

Index code

Figure 2 Power Control 1 Instruction

BS2-0: Set the LCD drive bias within the range from 1/2 to 1/13. Set the bias according to the LCD

drive duty cycle and LCD drive voltage.

BT3-0: Control the step-up factor of the step-up circuit. Adjust the step-up factor according to the

LCD drive duty and power-supply voltage to be used. Set the output of VLOUT1 to 5.5 V or lower.

DC2-0: Set the step-up cycle of the step-up circuit. When the cycle is accelerated, the driving ability

of the step-up circuit becomes high, but its current consumption is increased, too. Adjust the cycle

with consideration of the display quality and the current consumption.

AP1-0: Adjust the amount of fixed current from the fixed current source in the operational amplifier

circuit for the LCD drive-level power. When the amount of fixed current becomes large, the LCD

driving ability and the quality of the display become high, but the current consumption is increased.

Adjust the fixed current with consideration of the display quality and the current consumption. During

times when there is no display, such as in the sleep or standby modes, AP1-0 can be set to (0, 0) and

the current consumption is reduced by shutting the operational amplifier down.

SLP: Sets the sleep mode. When SLP = 1, bits AP1/0 and DISP in the first-screen driving-control

register are all fixed to 0. This stops the operation of the power-supply circuit and turns off the display

at the same time. The state of SLP bit does not change the values of these bits.

11