CS5505 Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS5505 Datasheet PDF : 40 Pages

| |||

CS5505/6/7/8

CS5505/6/7/8

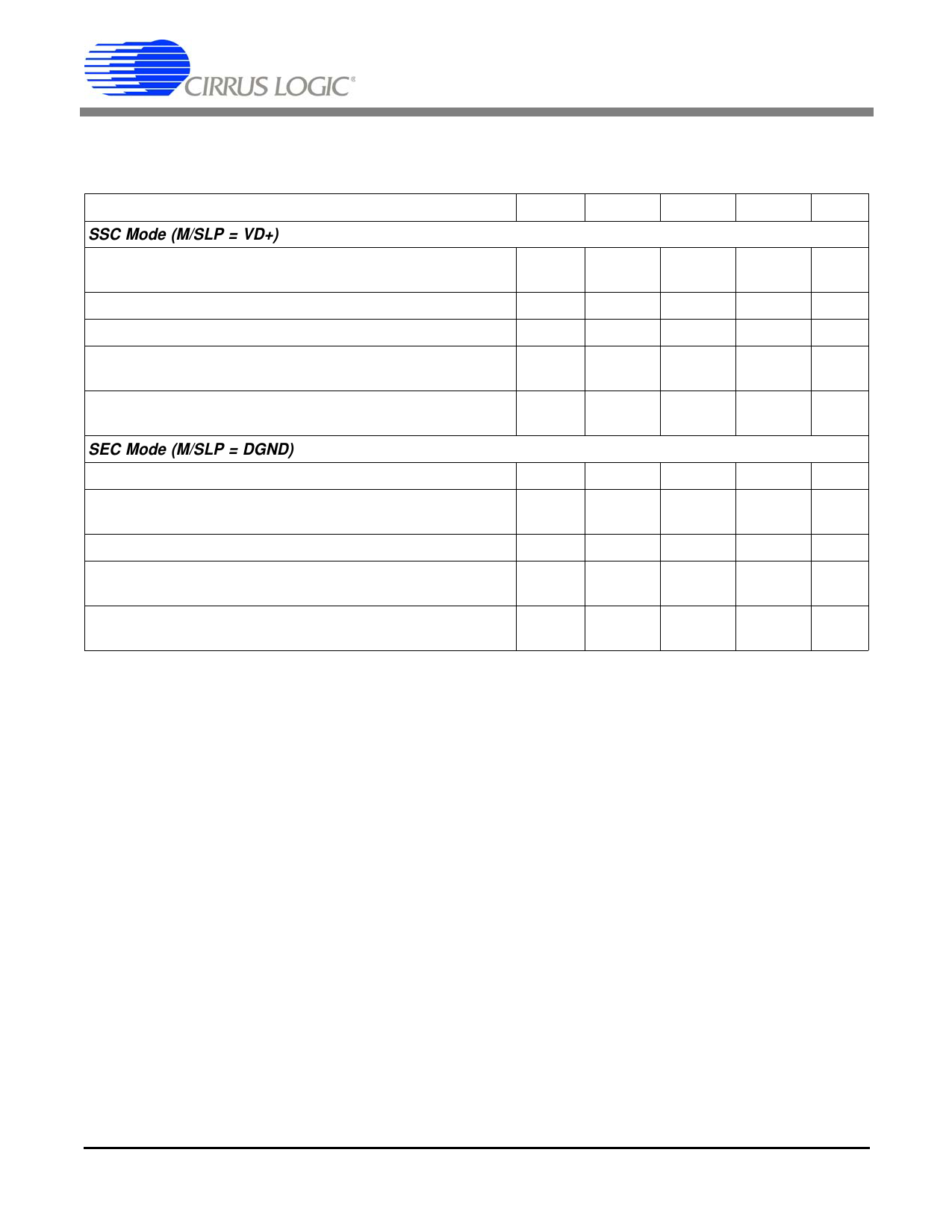

3.3V SWITCHING CHARACTERISTICS (TA = TMIN to TMAX VA+ = 5V ± 10%; VD+ = 3.3V ±

5%; VA- = -5V ± 10%; Input Levels: Logic 0 = 0V, Logic 1 = VD+; CL = 50 pF.) (Note 2)

Parameter

Symbol Min

SSC Mode (M/SLP = VD+)

Access Time:

CS Low to SDATA out (DRDY = low) tcsd1

-

DRDY falling to MSB (CS = low) tdfd

-

SDATA Delay Time:

SCLK falling to next SDATA bit tdd1

-

SCLK Delay Time

SDATA MSB bit to SCLK rising tcd1

-

Serial Clock (Out)

Pulse Width High tph1

-

Pulse Width Low tpl1

-

Output Float Delay:

CS high to output Hi-Z (Note 16) tfd1

-

SCLK rising to SDATA Hi-Z tfd2

-

SEC Mode (M/SLP = DGND)

Serial Clock (In)

fsclk

0

Serial Clock (In)

Pulse Width High tph2

200

Pulse Width Low tpl2

200

Access Time:

CS Low to data valid (Note 17) tcsd2

-

Maximum Delay time:

(Note 18)

SCLK falling to new SDATA bit tdd2

-

Output Float Delay:

CS high to output Hi-Z (Note 16) tfd3

-

SCLK falling to SDATA Hi-Z tfd4

-

Typ

Max Units

-

2/fclk

ns

2/fclk

3/fclk

ns

265

400

ns

1/fclk

-

ns

1/fclk

-

ns

1/fclk

-

ns

-

2/fclk

ns

1/fclk

-

ns

-

1.25 MHz

-

-

ns

-

-

ns

100

200

ns

400

600

ns

70

150

ns

320

500

ns

10

DS59F54