Z87L00 Просмотр технического описания (PDF) - Zilog

Номер в каталоге

Компоненты Описание

Список матч

Z87L00 Datasheet PDF : 50 Pages

| |||

Z87000/Z87L00

Spread Spectrum Controllers

FUNCTIONAL DESCRIPTION

The functional partitioning of the Z87000 is shown in Fig-

ure 2. The chip consists of a receiver, a transmitter, and

several additional functional blocks.

The receiver consists of the following blocks:

s Receive 1-bit ADC

s Demodulator, including:

– IF Downconverter

– AFC (Automatic Frequency Control)

– Limiter-Discriminator

– Matched Filter

– Bit Synchronizer

– Bit Inversion

– Frame Synchronizer (unique word detector)

– SNR Detector

s Receive Frame Timing Counter

s Receive Buffer and Voice Interface

The Transmitter Consists of the Following Blocks:

s Transmit Buffer and Voice Interface

s Transmit Frame Timing Counter (used on base station

only)

s Modulator, including:

– NCO

– Bit Inversion

Zilog

s Transmit 4-Bit DAC

In Addition, there are the following Shared Blocks.

s Event Trigger Block, Controlling:

– Transmit/Receive Switch

– Power On/Off Switches (Modulator, Demodulator,

RF Module)

– Antenna Switch Control (used on Base Station

only for Antenna Diversity)

s 4-Bit DAC for Setting Transmit Power Level

s 8-Bit ADC for Sampling the Received Signal Strength

Indicator (RSSI)

s DSP Core Processor

s Two 16-Bit General-Purpose I/O Ports

s Z87010 ADPCM Processor Interface

Basic Operation

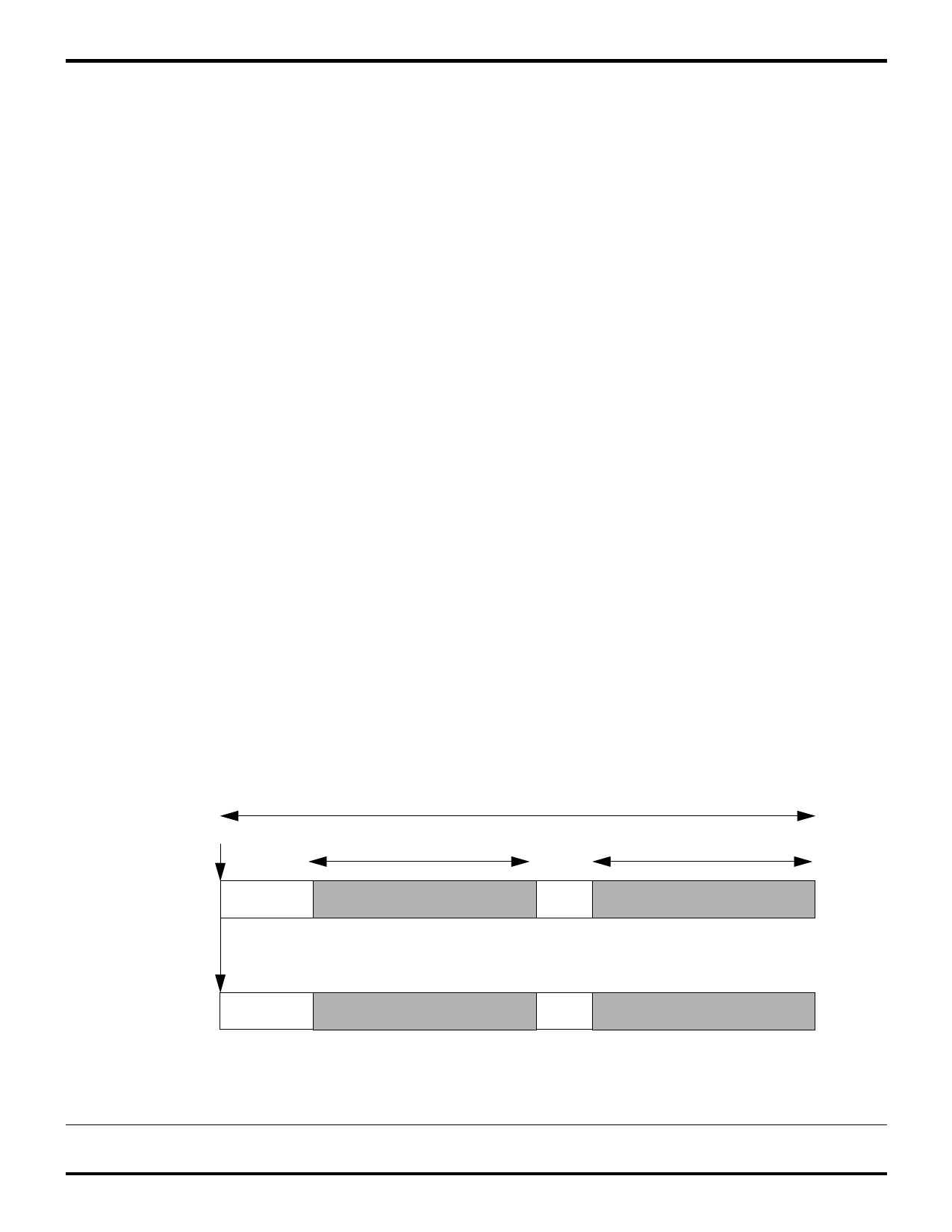

The transmitter and receiver operate in time-division du-

plex (TDD): handset and base station transmit and receive

alternately. The TDD duty cycle lasts 4 ms and consists of

the following events:

s At the beginning of the cycle, the frequency is changed

(hopping)

s The base station transmits a frame of 144 bits while the

handset receives

s The handset then transmits a frame of 148 bits while the

base receives.

HOP

BASE

Frequency

Hopping

guard time

HANDSET

144 bits

TX

RX

4ms frame

TDD switching

guard time

148 bits

RX

TX

Figure 1. Basic Time Duplex Timing

1-20

PRELIMINARY

DS96WRL0501