P4C1981L Просмотр технического описания (PDF) - Semiconductor Corporation

Номер в каталоге

Компоненты Описание

Список матч

P4C1981L Datasheet PDF : 13 Pages

| |||

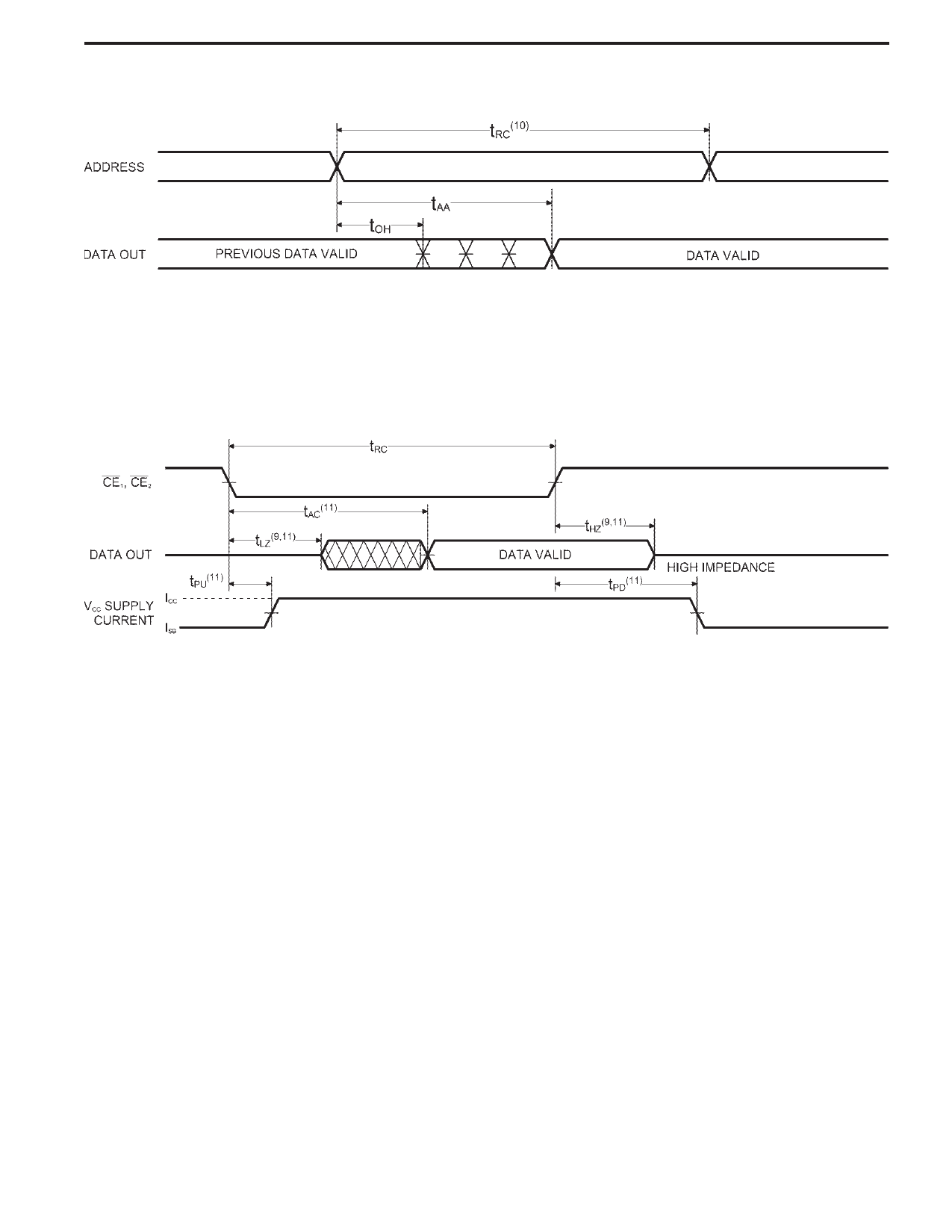

READ CYCLE NO. 2 (ADDRESS Controlled)(5,6)

P4C1981/1981L, P4C1982/1982L

READ CYCLE NO. 3 (CE1, CE2 Controlled)(5,7,8)

Note:

11. Transitions caused by a chip enable control have similar delays irrespective of whether CE1 or CE2 causes them.

Document # SRAM114 REV B

Page 5 of 13