CXB1585N Просмотр технического описания (PDF) - Sony Semiconductor

Номер в каталоге

Компоненты Описание

Список матч

CXB1585N Datasheet PDF : 14 Pages

| |||

CXB1585N

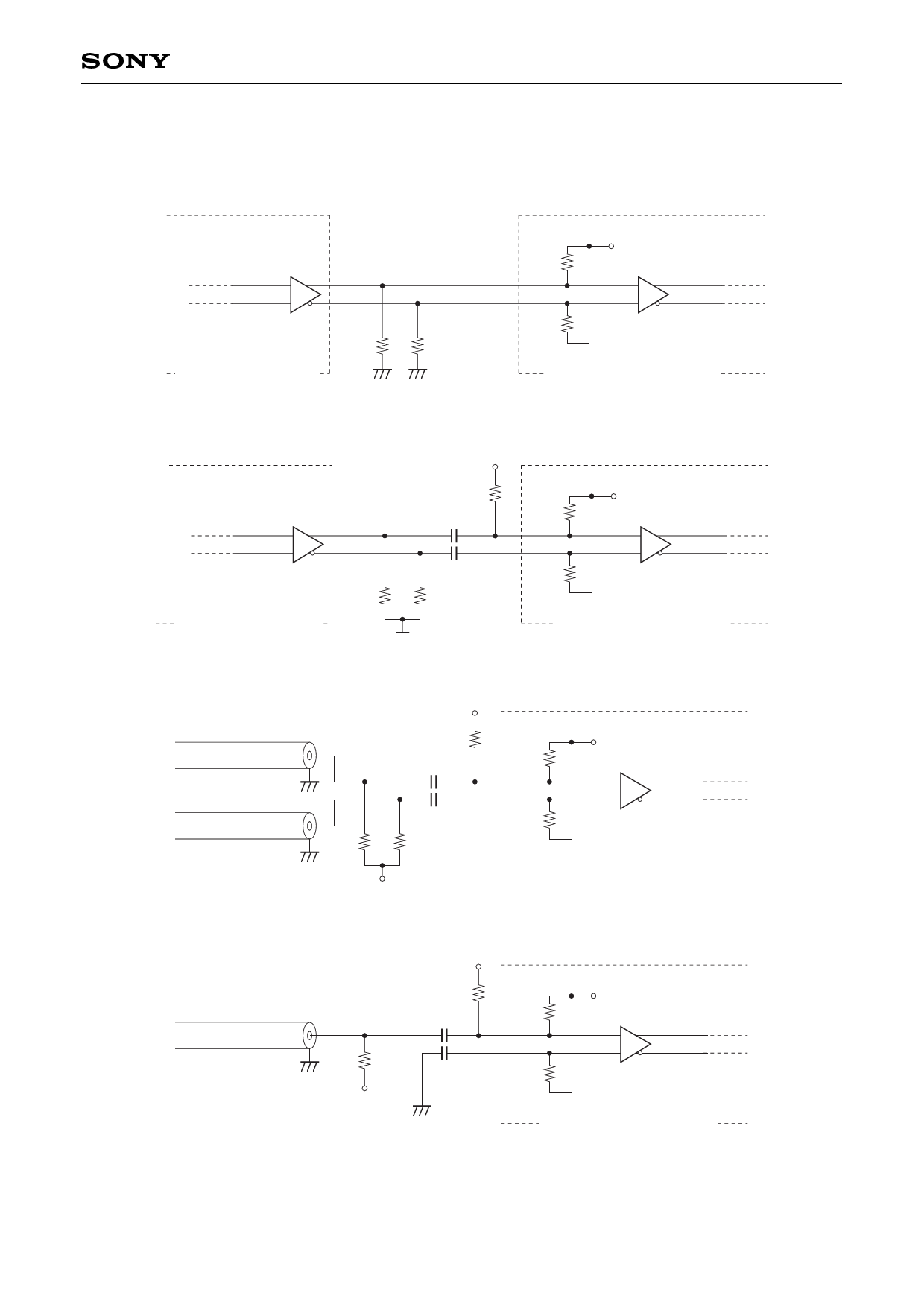

2. ECL input circuit

The ECL differential input pins are biased to VBB (VCC – 1.3V) via an 18kΩ resistor in the IC. See the figures

below for ECL differential input methods.

VCC = 3.3V, VEE = GND

VCC = 3.3V, VEE = GND

VBB (VCC – 1.3V)

18kΩ

3.3V ECL output buffer

160Ω

160Ω

18kΩ

ECL differential input buffer

(a) ECL differential signal from 3.3V ECL output buffer

VCC = GND, VEE = –4.5V

VCC

220kΩ

330pF

VCC = 3.3V, VEE = GND

18kΩ

VBB (VCC – 1.3V)

ECL100K output buffer

330Ω

330pF

330Ω

VEE

18kΩ

ECL differential input buffer

(b) ECL differential signal from ECL 100K output buffer

50Ω

TRANS.

LINE

VCC

220kΩ

330pF

VCC = 3.3V, VEE = GND

VBB (VCC – 1.3V)

18kΩ

330pF

50Ω

50Ω

18kΩ

VTT (VCC – 2V)

ECL differential input buffer

(c) ECL differential signal from 50Ω transmission line

VCC

220kΩ

330pF

VCC = 3.3V, VEE = GND

18kΩ

VBB (VCC – 1.3V)

50Ω

TRANS.

LINE

50Ω

330pF

VTT (VCC – 2V)

18kΩ

ECL differential input buffer

(d) ECL single signal from 50Ω transmission line

Fig. 2. ECL Input Circuits

– 10 –