PDI1394L21 Просмотр технического описания (PDF) - Philips Electronics

Номер в каталоге

Компоненты Описание

Список матч

PDI1394L21 Datasheet PDF : 52 Pages

| |||

Philips Semiconductors

1394 full duplex AV link layer controller

Preliminary specification

PDI1394L21

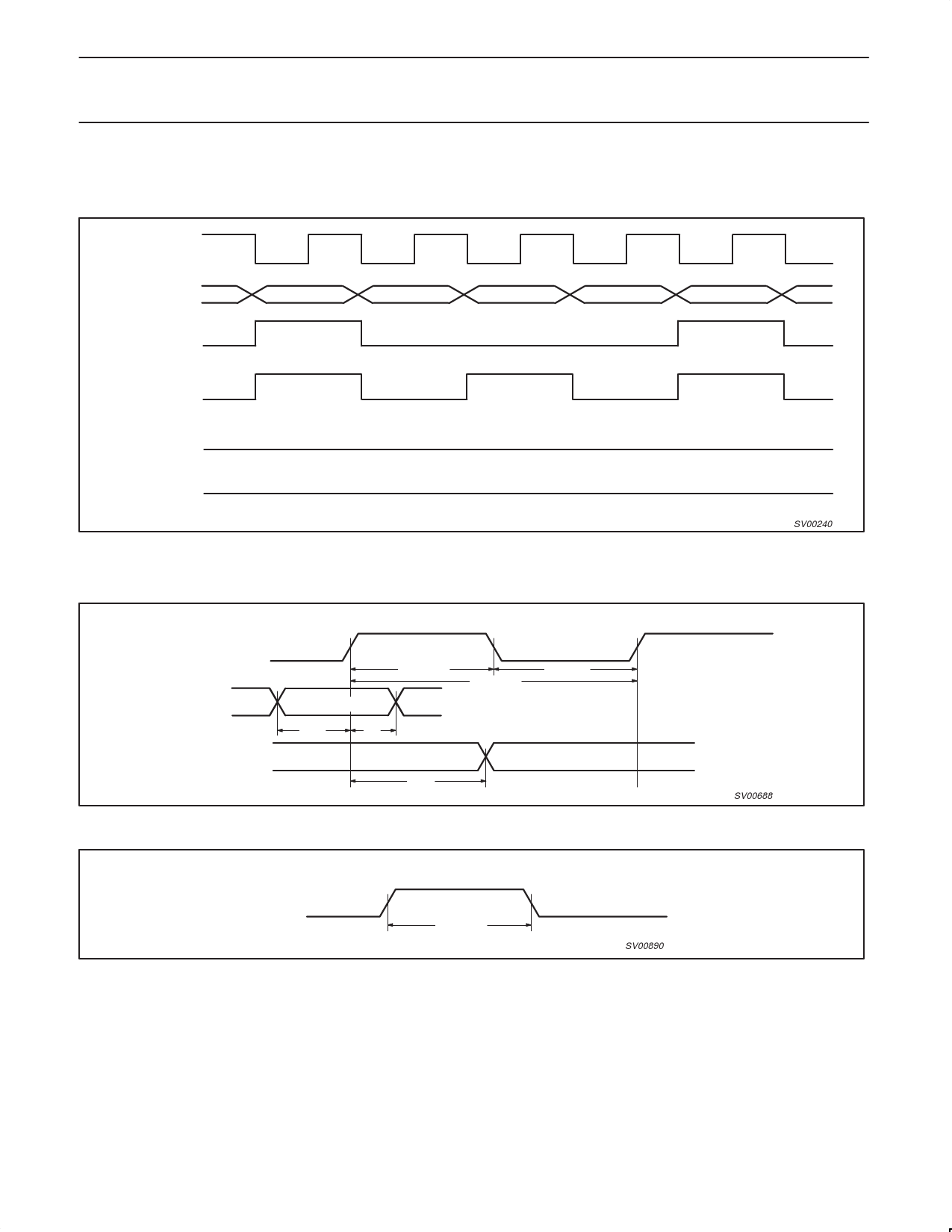

16.0 TIMING DIAGRAMS

16.1 AV Interface Operation

AVCLK

AV D[7:0]

MESSAGE

AVSYNC

INVALID DATA

MESSAGE

INVALID DATA

AVVALID

AVERR[0]

AVERR[1]

ASSERTED IN THE EVENT OF A BUS PACKET CRC ERROR

ASSERTED IN THE EVENT OF A DATA BLOCK SEQUENCE ERROR

Figure 25. AV Interface Operation Diagram

16.2 AV Interface Critical Timings

AVCLK

ÉÉÉ AV D [7:0], AVVALID,

ÉÉÉ AVSYNC, AVENDPCK

AV D [7:0], AVERR[1:0],

AVSYNC, AVVALID

ÉÉÉÉÉÉ VALID

tWHIGH

tSU

tIH

tOD

tPERIOD

tWLOW

VALID

Figure 26. AV Interface Timing Diagram

MESSAGE

SV00240

SV00688

AVxFSYNC

tPWFS

Figure 27. AVxFSYNC Timing Diagram

SV00890

1999 Aug 06

46