IDT72805LB(1996) Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT72805LB

(Rev.:1996)

(Rev.:1996)

IDT72805LB Datasheet PDF : 20 Pages

| |||

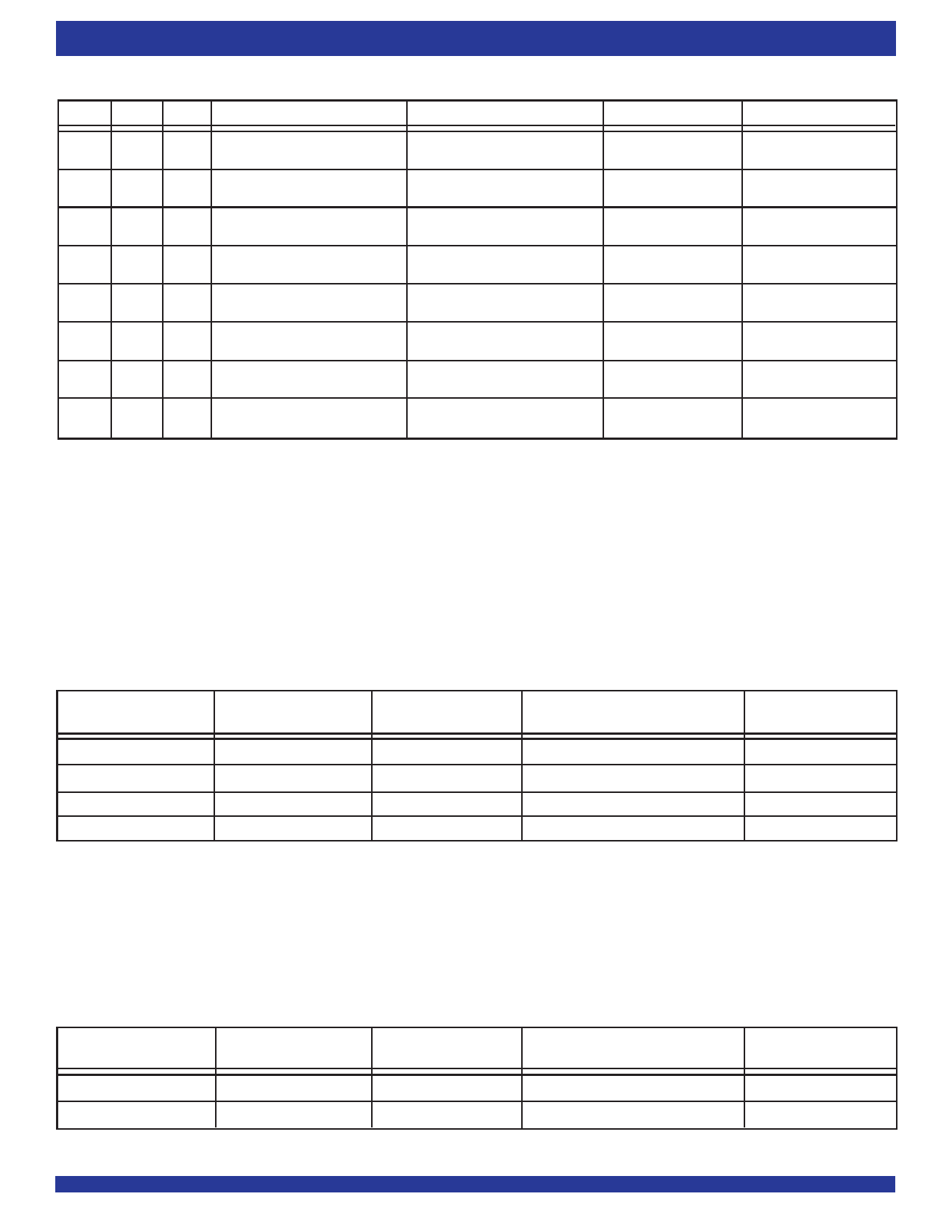

IDT72805/72815/72825 CMOS Dual SyncFIFO™

256 x 18-BIT, 512 x 18, and 1024 x 18

WCLK

t CLKH

t CLK

t CLKL

tDS

D0 - D17

WEN

DATA IN VALID

tENS

t WFF

FF

t SKEW1 (1)

RCLK

COMMERCIAL TEMPERATURE RANGE

t DH

tENH

t WFF

NO

OPERATION

REN

3139 drw 05

NOTE:

1. tSKEW1 is the minimum time between a rising RCLK edge and a rising WCLK edge to guarantee that FF will go HIGH during the current clock cycle. If the

time between the rising edge of RCLK and the rising edge of WCLK is less than tSKEW1, then FF may not change state until the next WCLK edge.

Figure 5. Write Cycle Timing

5.17

9